打印本文

打印本文  关闭窗口

关闭窗口 关键词:宽带无线接入网;RS码;FPGA;关键方程;欧式算法;IDFT

一、 引言

差错控制技术对提高通信系统的可靠性有重要作用。RS码具有很强的纠错能力,既可以纠随机错,又可以纠突发错,在通信系统中应用广泛。RS的编码方案相对简单,在此不赘述,仅在最后的测试过程中给出测试结果。但RS码的解码复杂度高,数学运算量大,国内的硬件及软件解码方案大多不能满足高速率的传输需求,一般适用于10 MHz以下。本文基于欧氏算法(Euclidean Algorithm)和IDFT相结合的RS解码方案利用FPGA芯片实现了GF(28)上符号速率为32.5 MHz的流式解码方案,最大延时为640 ns,参数可以根据需要灵活设置。

二、RS码的结构

对于码长为N=q-1,生成多项式为g(x)=(x

错,当符号速率为50 MHz时,可以在信道误比特率为10-3情况下,把误码率改善为10-7以下。

三、欧氏算法与IDFT结合的RS码译码方案

RS码是BCH码的子类。RS译码算法一般分为3步:伴随式的计算、关键方程的获得和错误图样的求解。如何由伴随式计算差错定位多项式是RS译码中最困难和最关键的一步。

联接多项式的求解方法很多,但欧氏算法数据存储量少,控制简捷;通过VC仿真也证明适合于硬件实现,因而曾被美CCSDS机构推荐使用。采用欧氏算法获取联接多项式,所需时间与错误个数成正比,而通常出现多个错误的概率远远低于少个错误,因此从时间上考虑,采用欧氏算法是较好的选择。

在获得关键方程以后,利用频域的处理方法,采用最短线性移存器的综合和IDFT变换的方法进行错误值的求解,逻辑单元简单,耗时少。虽然在IDFT时需要较多的资源,但对GF(2n)来说,当n<10的情况下,变换域译码器要比时域译码器简单得多[2]。

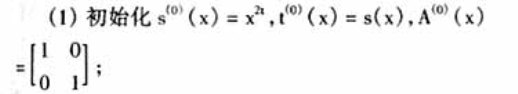

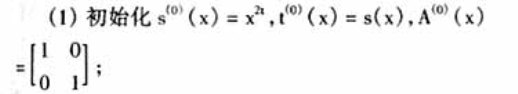

因而在课题中采用了Euclidean算法和频域处理相结合的方法,获得了较好的效果。Euclidean算法[3]步骤如下:

(2)按所列方法进行迭代

四、RS译码在FPGA上的实现

有限域乘法器和控制逻辑的设计在上述3个步骤中最为重要:有限域的运算速度是制约译码速度快慢的瓶颈,控制逻辑决定了译码的流程。硬件电路的软件开发工具给设计复杂电路提供了简捷的思路。本系统采用了QUARTUS与第三方软件相结合的方法,用VHDL语言设计了大部分功能模块。特别是在乘法器设计中,乘数确定、被乘数不定的乘法器以及乘数、被乘数均不定的有限域乘法器,经逻辑综合和优化设计后,运算速度可分别在6.8 ns 和11.6 ns内完成,完全可以满足系统符号速率50 MHz的要求。

1伴随式S0,S1,…,S2t-1的求解

令r1,r2,…,rn为接收到的RS码字,考虑到RS系统码监督矩阵的性质有:

由此可构造出乘法电路,如图1所示。

利用此简单的逻辑电路即可实现伴随式的计算,保证了接收码字在输入结束(小于3 ns)时,即可获得伴随式。当S0,S1,…,S2t-1均为0时,译码结束,给出标志。否则,启动步骤2;

2.利用伴随式计算差错定位多项式

在获得伴随式的基础上,可求解错误定位多项式:

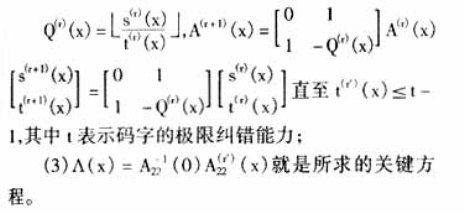

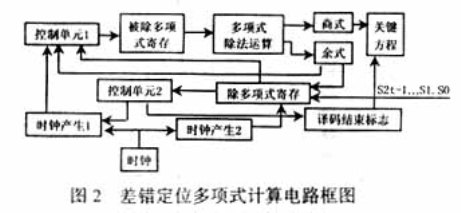

求解过程如图2所示。

从图2可以看出,当伴随式计算完毕后,在时钟上升沿送入控制单元2,使除数多项式寄存器初始化,同时控制单元1将被除数多项式寄存器初始化为x2t。控制单元1在时钟的驱动下,控制被除数多项式寄存器进行数据的更迭。控制单元2在时钟的驱动下控制除数多项式寄存器进行数据的代换。对输出的商多项式利用迭代得出关键方程。当输出的余式次数低于t=8时,计算结束,启动步骤3;同时,全系统清零,准备下一个过程的开始。

此种设计仅需2组寄存器和一组除法运算单元,资源耗费较少。框图中采用的并行算法和梯形拓扑结构保证了欧氏算法的速度。当t≤8时,每增加一个错误位置,耗费时间将增加80 ns。不过,由于少数错误出现的概率远远大于多个错误的概率,耗时与错误多少成正比的特性正是我们所期望的。

应该指出,系统速度的进一步提高受到求逆运算速度的限制,求逆运算没有明确的数学结构,通常采用查表的方法,这是制约速度提高的瓶颈。但针对流式译码,上述结构已能满足要求。

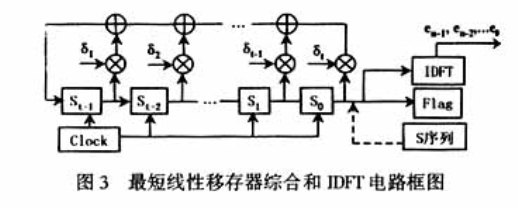

3.利用最短线性移存器综合和IDFT变换获取错误图样

硬件实现框图见图3。用St-1,St-2,…,S1,S0和σ(x)经循环迭代产生S0,…,St,St 1,…,Sn-2,Sn-1,即S序列,由此计算产生的St与经第一级伴随式电路产生的St进行比较,两者相等表示欧氏算法获得的σ(x)是正确的,此时Flag输出标志位“0”;不等则表示译码错误,输出标志位“1”。对S序列进行IDFT运算,可获得并行的错误图样en-1,en-2,…,e0;最后从缓存中读出接收码字,并与错误图样进行异或运算即可得到正确的码字。

完成整个计算只需要255个时钟周期,与时域译码算法相比要快得多。时域运算时,仅进行钱(Chien)搜索[1](钱闻天于1964年提出的求σ(x)根的一种实用方法)就需要255次运算,在每一次运算中还要进行8次多项式计算,当获得错误位置后,再进行错误值的求解,时间的耗费可见一斑。不过采用本文提供的方案,IDFT变换与S序列的求解需同步进行,占用的硬件资源较多,但资源的耗费却换取了速度的提高。

五、测试过程

1编码器的测试

测试时,采用时钟速率为50 MHz,在EN为高电平时输入信息有效;编辑仿真向量文件后,启动仿真,可得到如图4所示波形。为简单起见,输入信息缩短为3个GF(28)上符号。其中,输入输出码字每个符号均表示为2位16进制数。

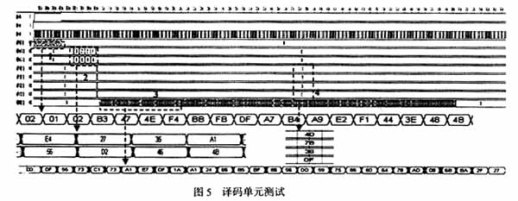

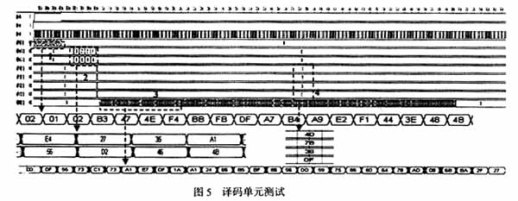

2.译码单元测试

对编码器的结果(02.01.02.B3.47.4E.F4.BB.FB.DF.A7.B4.A9.E2.F1.45.3F.49.4A)在最后4位设置错误,错误图样均为0X01即接收码字为(02.01.02.B3.47.4E.F4.BB.FB.DF.A7.B4.A9.E2.F1.44.3E.48.4B);伴随式的计算结果:S0,S1,…,S14,S15为(00.0F.55.73.C1.73.A1.E7.DF.1A.A1.24.66.B5.BF.86);欧氏算法的商结果:(E4,56)、(27,D2)、(35,46)、(A1,4B)分别对应域上

3IDFT变换单元的测试

IDFT变换单元的测试如图6所示。其中输入为S序列和时钟,B4、B3、B2、B1、X是分别对应于RS码的最后5个位置IDFT变换,与我们所设置的4个错误完全一致;经并/串变换与接收码字进行异或运算即得到正确的码字。整个过程同时由VC编程仿真,中间过程的监测表明设计正确无误。

六、结论

本方案在ALTERA公司的FLEX10KE系列的EPF10K130EQC240-1芯片上得到了实现,适宜于离散译码、流式译码,在添加一级缓存的情况下,同样适宜于连续译码。符号速率可以达到50 MHz以上(上述验证的时钟是50 MHz),达到了预期的设计要求。

参考文献

[1]王新梅,肖国镇.纠错码-原理与方法[M].西安:西安电子科技大学出版社,2001

[2]I S Reed.A Comparison of VLSI Architecture for Time and Transform Domain Decoding of Reed-Solomon Codes[R].California:University of Southern California,1990.

[3]I S Reed.A Single Chip VLSI Reed-Solomon Decoder[R].California:University of Southern California,1990.

[4]I S Reed.A VLSI Single Chip (255,233) Reed-Solomon Encoder[R].California:University of Southern California,1990.

[5]赵雅兴.FPGA原理、设计与应用[M].天津:天津大学出版社,1999

[6]侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2001

打印本文

打印本文  关闭窗口

关闭窗口